![]()

![]()

![]()

Use LEFT and RIGHT arrow keys to navigate between flashcards;

Use UP and DOWN arrow keys to flip the card;

H to show hint;

A reads text to speech;

155 Cards in this Set

- Front

- Back

|

|

|

|

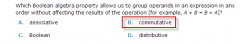

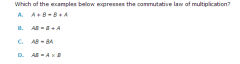

A * B = ?

|

B * A

(Commutative) |

|

|

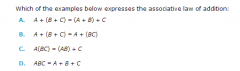

A + (B+C)= ?

|

(A+B)+C

(Associative) |

|

|

A(BC) = ?

|

(AB)C

(Associative) |

|

|

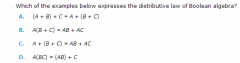

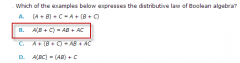

A(B+C) = ?

|

AB + AC

(Distributive) |

|

|

(A+B)(C+D) = ?

|

AC + AD + BC +BD

(Distributive) |

|

|

//A = ?

|

A

(Double Inversion) |

|

|

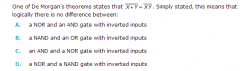

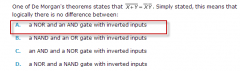

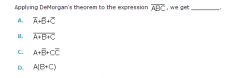

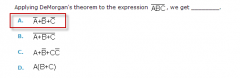

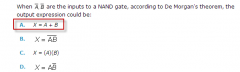

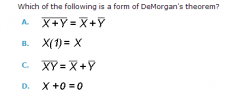

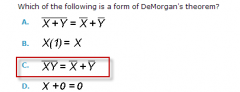

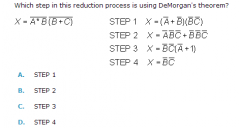

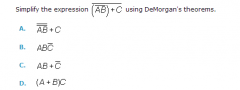

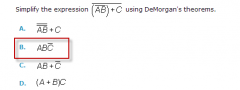

/(AB) = ?

|

/A+/B

(DeMorgan) |

|

|

/(A+B) = ?

|

/A/B

(DeMorgan) |

|

|

A + AB = ?

|

A

|

|

|

(A+B)(A+C) = ?

|

A+BC

|

|

|

A+/AB = ?

|

A+B

|

|

|

A * 0 = ?

|

0

(AND) |

|

|

A * 1 = ?

|

A

(AND) |

|

|

A * A = ?

|

A

(AND) |

|

|

A * /A = ?

|

0

(AND) |

|

|

A + 0 = ?

|

A

(OR) |

|

|

A + 1 = ?

|

1

(OR) |

|

|

A + A = ?

|

A

(OR) |

|

|

A + /A = ?

|

1

(OR) |

|

|

A (+) 0 = ?

|

A

(XOR) |

|

|

A (+) 1 = ?

|

/A

(XOR) |

|

|

A (+) A = ?

|

0

(XOR) |

|

|

A (+) /A = ?

|

1

(XOR) |

|

|

A decoder is defined as

|

a circuit which converts an n-bit input codeword into m lines of output, where m is less than or equal to 2^n

|

|

|

An encoder is defined as

|

a circuit which converts n lines of input into a m-bit codeword, where n is less than or equal to 2^m.

|

|

|

A demultiplexer is defined as

|

gates one input of data line to one out of 2^n output lines.

|

|

|

A multiplexer is defined as

|

gates one of 2^n data inputs to a single output, which is just the opposite operation of a demultiplexer.

|

|

|

Read-Only Memories (ROM's) are constructed from which of the following components?

|

A DECODER and an ENCODER

|

|

|

If a sequential circuit possesses N memory elements (binary cells or flip flops), what is the maximum number of states could it have?

|

2^N

|

|

|

In general, the PRESENT STATE of a sequential logic circuit is determined by the

|

MEMORY ELEMENTS

|

|

|

What are the 2 D flip-flop operations

|

D = 0 is RESET: Qn+1 = 0

D = 1 is SET: Qn+1 = 1 |

|

|

Anything AND'ed with a 0 is equal to....

|

0

|

|

|

Anything AND'ed with a 1 is equal to...

|

itself

|

|

|

Anything OR'ed with a 0 is equal to...

|

itself

|

|

|

Anything OR'ed with a 1 is equal to...

|

1

|

|

|

Anything AND'ed with itself is equal to....

|

itself

|

|

|

Anything OR'ed with itself is equal to....

|

itself

|

|

|

NOT Gate

|

Takes a bit as input and produces opposite as output

A Q 0 1 1 0 |

|

|

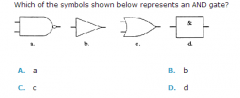

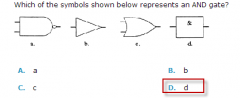

AND Gate

|

If A is 1 AND B is 1, output Q should be 1

A B Q 0 0 0 1 0 0 0 1 0 1 1 1 |

|

|

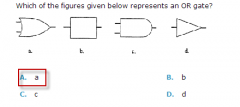

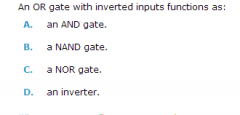

OR Gate

|

If A is 1 OR B is 1 OR Both are 1 then Q is 1

A B Q 0 0 0 1 0 1 0 1 1 1 1 1 |

|

|

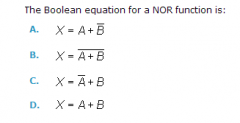

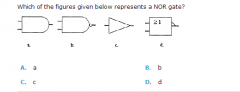

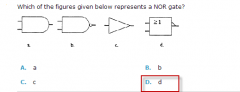

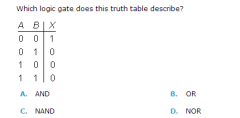

NOR Gate

|

(NOT and OR, or OR inverted)

A B Q 0 0 1 1 0 0 0 1 0 1 1 0 |

|

|

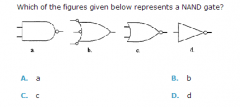

NAND Gate

|

(NOT and AND, or AND inverted)

A B Q 0 0 1 1 0 1 0 1 1 1 1 0 |

|

|

XOR Gate

|

Exclusive OR. If either A OR B is 1, but not both, Q is 1

A B Q 0 0 0 1 0 1 0 1 1 1 1 0 |

|

|

XNOR Gate

|

If both A and B are the same, Q is 1

(Easiest to think of as an inverted XOR) A B Q 0 0 1 1 0 0 0 1 0 1 1 1 |

|

|

Muxes, Decoders, and full adders are ________ logic circuits

|

Combinational Logic Circuts

|

|

|

Building blocks for finite state machines

|

Sequential Logic Circuits

|

|

|

Have no capacity of storing information

|

Combinational Logic Circuits

|

|

|

What does FSM stand for?

|

Finite State Machine

|

|

|

What does an FSM consist of ?

|

1. finite number of states

2. finite number of external inputs 3. finite number of external outputs 4. Specification of all possible state transitions 5. specification of what determines each external output value |

|

|

A State Diagram or Finite-State-Machine (FSM) is?

|

- A way to describe desired behavior of sequential circuit

- List states, and transitions among states |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

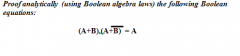

AA+A!B+BA+B!B

A+A!B+BA+0 (A!B+BA) = A A+A+0 A |

|

|

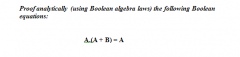

A+B = A+!A*B

A(A+!AB) AA+A!AB A+(A!A=0)B A+0*B A |

|

|

A(+)B = A*!B+!A*B

A(+)A = A*!A+!A*A 0+0 = 0 |

|

|

|

|

|

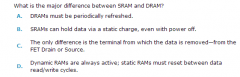

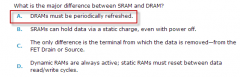

Primary memory is ______

|

Volatile

|

|

|

Cache Memory also known as

|

Static RAM (SRAM)

|

|

|

What is the memory element for SRAM?

|

Flip flop - 6 to 8 transistors

|

|

|

What are the advantages of SRAM

|

- Stable memory function

- Fast Access |

|

|

What are the disadvantages of SRAM?

|

- High power consumption

- High Price - Low Density |

|

|

Main memory is usually known as

|

Dynamic RAM (DRAM)

|

|

|

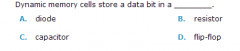

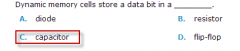

What is the memory element for DRAM?

|

1 transistor and a parasitic Capacitor (Charged capacitor is 1, discharged is 0)

|

|

|

What are the disadvantages of DRAM?

|

- Unstable memory function

- Noise sensitive capacitor - Whole memory discharge - Capacitor needs recharged every 5 milliseconds - Slow Access time because of refresh rate |

|

|

What are the advantages to DRAM

|

- High density (1 transistor)

- High Capacity - Low Price - Less power consumption |

|

|

A(+)B

|

A*!B+!A+B

|

|

|

A!B+!AB

|

A(+)B

|

|

|

A(+)A

|

A*!A+!AA = 0

so 0!!!! |

|

|

A+0

|

A

|

|

|

A*1

|

A

|

|

|

A+1

|

1

|

|

|

A*0

|

0

|

|

|

A+!A

|

1

|

|

|

A*!A

|

0

|

|

|

A+B

|

BA

|

|

|

A+(B+C)

|

(A+B)+C

A+B+C |

|

|

A*(B*C)

|

(A*B)*C = A*B*C

|

|

|

A(B+C)

|

A*B+A*C

|

|

|

AB+AC

|

A(B+C)

|

|

|

A+(B*C)

|

(A+B)*(A+C)

|

|

|

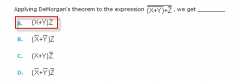

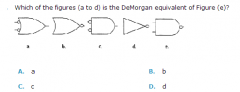

_____

A*B |

__ __

A + B |

|

|

____

A+B |

___ __

A * B |

|

|

A+A

|

A

|

|

|

A*A

|

A

|

|

|

!A*B+A*B

|

B

|

|

|

A+!A*B

|

A+B

|

|

|

A*(A+B)

|

A

|