![]()

![]()

![]()

Use LEFT and RIGHT arrow keys to navigate between flashcards;

Use UP and DOWN arrow keys to flip the card;

H to show hint;

A reads text to speech;

10 Cards in this Set

- Front

- Back

|

CISC |

Complex instruction set computer: Indica un architettura per microprocessori formata da un set d'istruzioni contente istruzioni in grado di eseguire operazioni complesse come la lettura di un dato in memoria, la sua modifica e il suo salvataggio direttamente in memoria. Un esempio di architettura CISC è l' X86 di Intel e AMD |

|

|

RISC |

Reduced Instruction Set computing: Indica un tipo di architettura per microprocessori che predilige lo sviluppo di un' architettura semplice e lineare, permettendo di realizzare microprocessori in grado di eseguire set d'istruzioni in tempi minori rispetto a una classica CISC |

|

|

CU |

Control unit: è un componente delle cpu che ha il compito di coordinare tutte le azioni necessarie per l'esecuzione di una istruzione e di insieme di istruzioni. Le azioni che coordinano i vari settori della CPU vengono dette micro-operazioni o micro-istruzioni. Un insieme di micro-istruzioni è detto micro programma. La CU si occupa anche di convertire le istruzioni in linguaggio macchina in segnali per il datapath, supervisiona la corretta sequenza di operazioni per un'istruzione(Read, Write), controlla le operazioni dell'ALU |

|

|

DATAPATH |

E' un insieme di unità di calcolo, come: ALU, registri, moltiplicatori necessari per l'esecuzione delle istruzioni della CPU. Il passaggio di due operandi attraverso la ALU e la memorizzazione del risultato in un nuovo registro viene detto ciclo di data path. |

|

|

MMU |

Memory management unit: Classe di componenti HW, che gestisce le richieste di accesso alla memoria generate dalla CPU |

|

|

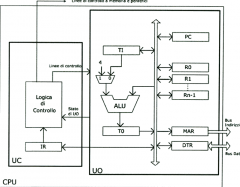

Organizzazione CPU(Disegno) |

|

|

|

Registri della CPU |

PC: program Counter, contiene l'indirizzo della prossima istruzione che si dovrà eseguire CSR: Control and Status Register, indica il buon esito dell'ultima operazione eseguita o eventuali stati di errore IR: Istruction Register Istruzione in corso di decodifica prima dell'esecuzione MAR: Memory Address Register contiene l'indirizzo della cella di memoria RAM a cui accedere per leggere o scrivere il dato MDR: Memory Data Register per il transito del dato da/verso la memorio o dell'istruzione letta dalla memoria Registro degl'interupt Registro per puntatori: Contiene indirizzi fisici di locazioni della memoria principale |

|

|

FSB |

Front Side Bus: E' il bus che si occupa di mettere in comunicazione la CPU con il northbridge. la banda passante si calcola moltiplicando i byte delle word del processore per la frequenza di clock(cicli al secondo) per il numero di data transfer ad ogni ciclo. |

|

|

HyperTransport |

E' un tipo di Bus bidirezionale seriale/parallelo a bassa latenza introdotto nel 2001 usato nei processori AMD, Nvidia, VIA, Sis e HP. |

|

|

QuickPath Interconnect |

Indica un tipo di BUS introdotto nel 2008 dalla INTEL ed è un BUS introdotto per migliorare la compatibilità HW tra processori diversi per eventuali sostituzioni. Lo scopo è quello di permettere alla CPU di comunicare direttamente con le varie componenti della MOTHERBOARD riducendo in questo modo la latenza e aumentando la banda passante maggiore. |